# GPU-accelerated CFD Simulations for Turbomachinery Design Optimization

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 2 oktober 2017 om 10:00 uur

door

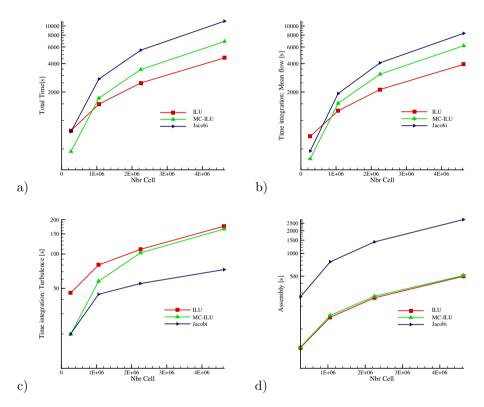

Mohamed Hassanine AISSA Diplom in Aerospace Engineering, University of Stuttgart, Germany

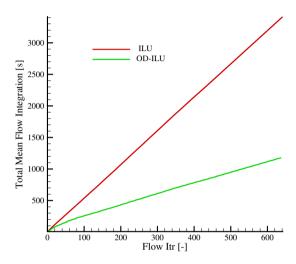

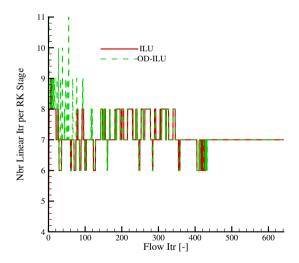

geboren te Nabeul, Tunesië

Dit proefschrift is goedgekeurd door de

Promotor: Prof.dr.ir. C. Vuik Copromotor: Dr.ir. T. Verstraete

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof.dr.ir. C. Vuik, Technische Universiteit Delft, promotor Dr.ir. T. Verstraete, Von Karman Institute, Belgium, copromotor

#### Onafhankelijke leden:

Prof.dr. S. Hickel Technische Universiteit Delft, The Netherlands

Prof.dr.ir. C.W. Oost- CWI and Technische Universiteit Delft , The Netherlands

erlee

Prof.dr.ir. B. Koren Technische Universiteit Eindhoven, The Netherlands

Prof.dr. S.F. Portegies Universiteit Leiden, The Netherlands

Zwart

Dr. A. Lani Von Karman Institute, Belgium

GPU-accelerated CFD Simulations for Turbomachinery Design Optimization

Dissertation at Delft University of Technology.

Copyright © 2017 by M.H. Aissa

The work described in this thesis has received funding from the European Union Seventh Framework Programme (FP7/2007-2013), Marie Curie Initial Training Networks (ITN) action, under grant agreement no. 316394, AMEDEO. This work was also partially funded by VLAIO in the framework of the SBO EUFORIA project (IWT-140068). The support is gratefully acknowledged.

ISBN 978-2-87516-123-9

Published by: The Von Karman Institute for Fluid Dynamics with permission

## **Contents**

| 36 | amen                                                     | vatting                                                              | VII |

|----|----------------------------------------------------------|----------------------------------------------------------------------|-----|

| Sı | ımm                                                      | ary                                                                  | ix  |

| A  | ckno                                                     | wledgment                                                            | хi  |

| 1  | Intr                                                     | roduction                                                            | 1   |

|    | 1.1                                                      | CFD and automated optimization                                       | 1   |

|    | 1.2                                                      | High-Performance Computing                                           | 4   |

|    | 1.3                                                      | Research objectives                                                  | 6   |

|    | 1.4                                                      | Context and outline of the thesis                                    | 8   |

| 2  | Graphics Processing Units for High Performance Computing |                                                                      |     |

|    | 2.1                                                      | Introduction                                                         | 11  |

|    | 2.2                                                      | From graphics pipelines to High Performance Computing                | 12  |

|    | 2.3                                                      | GPUs: a throughput-oriented latency-tolerant HPC device              | 14  |

|    | 2.4                                                      | CUDA: a programming language and an execution model                  | 15  |

|    | 2.5                                                      | Memory hierarchy of the GPU                                          | 21  |

|    | 2.6                                                      | Profiler-Driven code optimization                                    | 24  |

|    | 2.7                                                      | Conclusion                                                           | 27  |

| 3  | Literature Review: Use of the GPU in Design Optimization |                                                                      |     |

|    | 3.1                                                      | Introduction                                                         | 29  |

|    | 3.2                                                      | Topology optimization                                                | 30  |

|    |                                                          | 3.2.1 Solid Isotropic Microstructure with Penalization method (SIMP) | 31  |

|    |                                                          | 3.2.2 Level-Set method                                               | 33  |

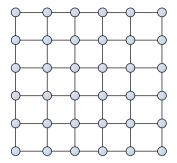

|    |                                                          | 3.2.3 Underlying FEM                                                 | 33  |

|    | 3.3                                                      | Shape optimization                                                   | 36  |

|    | 3.4                                                      | Multidisciplinary Design Optimization (MDO)                          | 39  |

|    | 3.5                                                      | GPU in meta-heuristics                                               | 39  |

|    | 3.6                                                      | Discussion                                                           | 40  |

|    | 3.7                                                      | Conclusion                                                           | 40  |

| 4 | $\mathbf{GP}$                                                  | U-accelerated Simulations with Explicit Time-Stepping               | 43  |  |  |  |

|---|----------------------------------------------------------------|---------------------------------------------------------------------|-----|--|--|--|

|   | 4.1                                                            | Reynolds-Averaged Navier-Stokes Equations                           | 43  |  |  |  |

|   | 4.2                                                            | Implementation and discussion                                       | 45  |  |  |  |

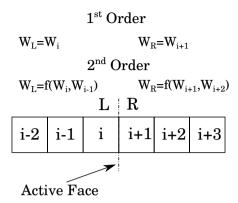

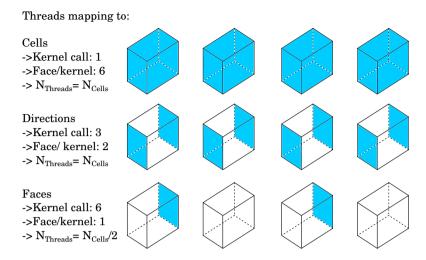

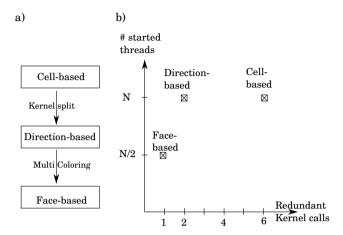

|   |                                                                | 4.2.1 The convective flux evaluation                                | 45  |  |  |  |

|   |                                                                | 4.2.2 Viscous flux                                                  | 58  |  |  |  |

|   |                                                                | 4.2.3 Boundary conditions                                           | 63  |  |  |  |

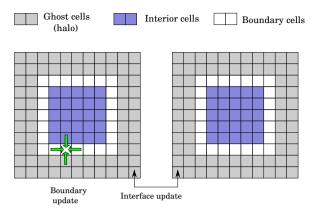

|   |                                                                | 4.2.4 Interface update                                              | 63  |  |  |  |

|   |                                                                | 4.2.5 Runge-Kutta stages                                            | 65  |  |  |  |

|   |                                                                | 4.2.6 Convergence acceleration techniques                           | 67  |  |  |  |

|   | 4.3                                                            | Validation and benchmark                                            | 72  |  |  |  |

|   | 4.4                                                            | Conclusion                                                          | 75  |  |  |  |

| 5 | GP                                                             | U-accelerated Simulations with Implicit Time-Stepping               | 77  |  |  |  |

| • | 5.1                                                            | Introduction                                                        | 78  |  |  |  |

|   | 5.2                                                            | Numerical scheme                                                    | 79  |  |  |  |

|   | 5.3                                                            | Preconditioned Krylov solvers                                       | 80  |  |  |  |

|   | 5.4                                                            | Flow solver implementation                                          | 85  |  |  |  |

|   |                                                                | 5.4.1 System assembly                                               | 85  |  |  |  |

|   |                                                                | 5.4.2 Linear solver with <i>on-demand</i> factorization             | 100 |  |  |  |

|   | 5.5                                                            | Results                                                             | 111 |  |  |  |

|   | 5.6                                                            | Discussion                                                          | 114 |  |  |  |

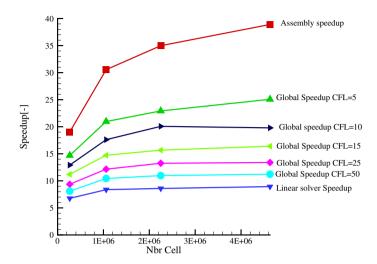

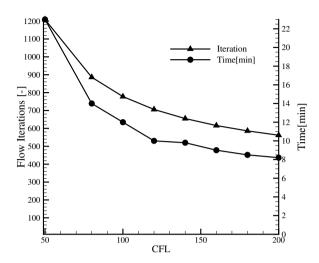

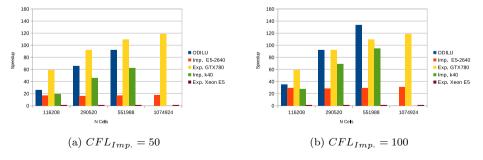

|   | 0.0                                                            | 5.6.1 Effect of the CFL number on the GPU speedup                   | 115 |  |  |  |

|   |                                                                | 5.6.2 Effect of the RK stages number on the GPU speedup             | 115 |  |  |  |

|   |                                                                | 5.6.3 Effect of the linear solver stop condition on the GPU speedup | 116 |  |  |  |

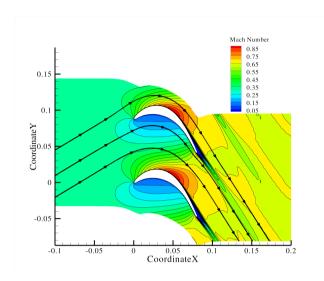

|   | 5.7                                                            | Validation                                                          | 116 |  |  |  |

|   | 5.8                                                            | Summary                                                             | 118 |  |  |  |

|   | 5.9                                                            | Conclusion                                                          | 118 |  |  |  |

| 6 | Explicit versus Implicit CFD Simulations, the GPU dimension 13 |                                                                     |     |  |  |  |

|   | 6.1                                                            | Introduction                                                        | 119 |  |  |  |

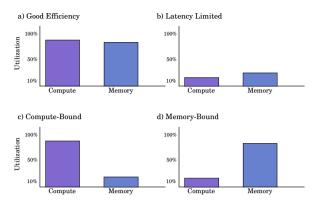

|   | 6.2                                                            | The classification                                                  | 122 |  |  |  |

|   | 6.3                                                            | Acceleration of the time integration method                         | 127 |  |  |  |

|   | 6.4                                                            | Numerical experiments: the subsonic turbine cascade T106C           | 130 |  |  |  |

|   | 6.5                                                            | Discussion                                                          | 135 |  |  |  |

|   | 6.6                                                            | Conclusion                                                          | 136 |  |  |  |

| 7 | App                                                            | plications: GPU CFD solvers in Design Optimization                  | 137 |  |  |  |

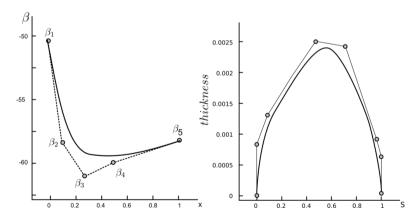

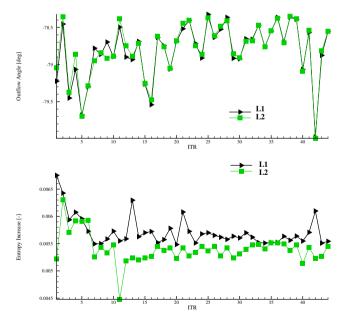

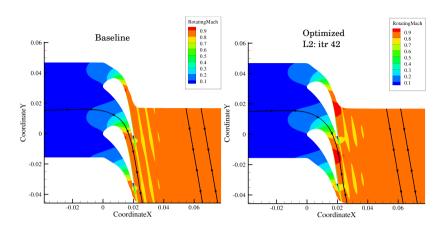

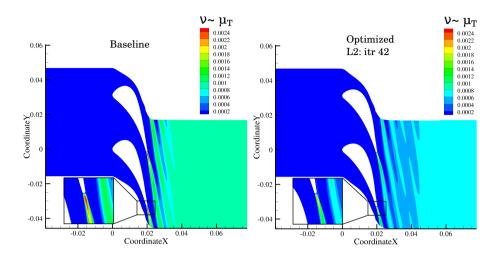

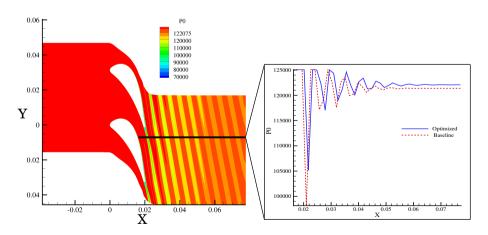

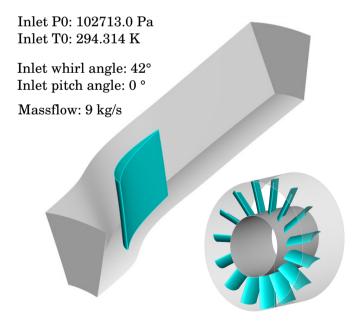

|   | 7.1                                                            | One-level optimization of a supersonic compressor cascade           | 137 |  |  |  |

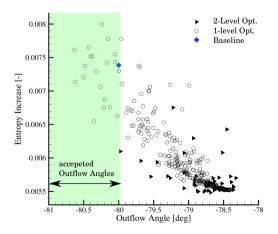

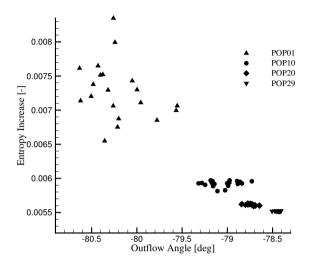

|   | 7.2                                                            | Metamodel-assisted optimization using Kriging                       | 140 |  |  |  |

|   |                                                                | 7.2.1 Kriging                                                       | 140 |  |  |  |

|   |                                                                | 7.2.2 The LS82 cascade                                              | 143 |  |  |  |

|   | 7.3                                                            | Final remarks                                                       | 145 |  |  |  |

| 8 | Conclusions 14                                                 |                                                                     |     |  |  |  |

|   | 8.1                                                            | Future work                                                         | 151 |  |  |  |

|   |                                                                | 8.1.1 Convergence acceleration of explicit solver                   | 151 |  |  |  |

|   |                                                                | 8.1.2 Metamodeling on the GPU                                       | 151 |  |  |  |

| $\mathbf{A}$     | A Appendix: Used Test cases            |                                      |     |  |  |  |  |

|------------------|----------------------------------------|--------------------------------------|-----|--|--|--|--|

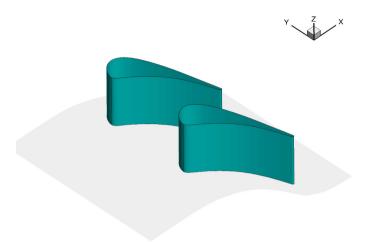

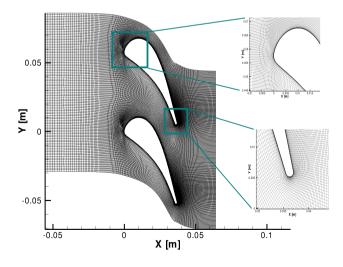

|                  | A.1                                    | Turbine inlet guide vane: LS89       | 153 |  |  |  |  |

|                  | A.2                                    | Compressor stator cascade: CC2D      | 155 |  |  |  |  |

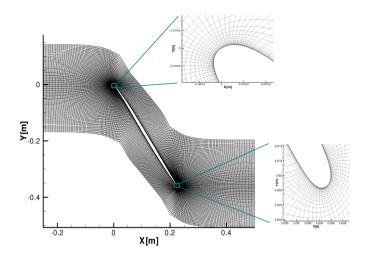

|                  | A.3                                    | Turbine stator cascade: T106C        | 155 |  |  |  |  |

|                  | A.4                                    | 3D Compressor stator blade: Turbolab | 155 |  |  |  |  |

| Curriculum vitae |                                        |                                      |     |  |  |  |  |

| Li               | List of publications and presentations |                                      |     |  |  |  |  |

## Samenvatting

Ontwerp optimalisatie is sterk afhankelijk van tijdrovende simulaties, vooral bij het gebruik van gradintvrije methodes. Deze methoden vereisen een groot aantal simulaties om een merkbare verbetering te krijgen op bestaande ontwerpen, die tegenwoordig op basis van de geaccumuleerde kennis over de jaren heen vaak reeds optimaal zijn.

High Performance Computing (HPC) is essentieel om de uitvoeringstijd van simulaties te verminderen. Terwijl parallelle programmering met behulp van de CPU gevestigd is sinds meer dan twee decennia, is het gebruik van andere technieken, zoals de Graphics Processing Unit (GPU), relatief recent in het domein van ontwerpoptimalisatie. De GPU heeft eigenlijk een enorme rekenkracht die vergelijkbaar is met een cluster van verschillende CPUs maar geconcentreerd in slechts n apparaat. Deze rekenkracht is evenwel niet gemakkelijk te gebruiken, aangezien volledige delen van de broncode moeten herschreven worden in een GPU-programmeertaal. Hoewel hoog-niveau programmeertalen (bijvoorbeeld openACC) een versnelling met een lage ontwikkelingskost kunnen realiseren, is het niet eenvoudig om met deze methoden grote snelheden te krijgen. Programma-talen op laag niveau zijn efficinter, maar er worden verschillende versnellingen gemeld en er is behoefte aan een diepere analyse om het GPU-potentieel transparanter te maken voor wetenschappers, vooral niet-experts in HPC.

Om de GPU-versnelling voor stationaire CFD-simulaties te bestuderen, zijn twee verschillende technieken binnen de GPU ingevoerd; n met expliciete en de tweede met impliciete tijdsintegratie. Na de overdracht en de validatie van de CPU-code naar de GPU, leidt de GPU-code optimalisatie tot het identificeren van een reeks sleutelparameters die de GPU-efficintie benvloeden. Tegelijkertijd zijn beide methoden vergeleken, wat resulteert in een prestatiemodel en een classificatie van de GPU-versnelling van sommige CFD-operaties. Het doel is om wetenschappers in staat te stellen een beslissing te nemen over de GPU-overdracht van hun CPU-applicaties door een GPU-versnelling te voorspellen.

Naast de twee GPU CFD-codes die nu gentegreerd zijn in het optimalisatie softwarepakket ontwikkeld in het VKI, verschafte dit onderzoek sleutelelementen om de dubbelzinnigheid over het GPU-potentieel te verminderen, namelijk een kwalitatieve analyse en een classificatie. Deze hulpmiddelen kunnen helpen bij het selecteren van de beste kandidaat voor een doorbraak in CFD-acceleratie. Tegelijkertijd identificeerde dit werk ernstige beperkingen bij de preconditioning van een lineair systeem van vergelijkingen en de limiet van hedendaagse iteratieve matrixfactorisatiemethoden met betrekking tot stabiliteit en convergentie. Er is nood aan een paradigma verschuiving naar inherente parallelle preconditioners.

De ontwikkelde codes werden getest op het optimaliseren van een compressor en een turbine cascade, dewelke resulteerden in een sneller optimalisatieproces op de GPU.

### **Summary**

Design optimization relies heavily on time-consuming simulations, especially when using gradient-free optimization methods. These methods require a large number of simulations in order to get a remarkable improvement over reference designs, which are nowadays based on the accumulated engineering knowledge already quite optimal.

High-Performance Computing (HPC) is essential to reduce the execution time of the simulations. While parallel programming using the CPU is established since more than two decades, the use of accelerators, such as the Graphics Processing Unit (GPU), is relatively recent in design optimization. The GPU has actually a huge computational power comparable to a many-core cluster but concentrated in one device. This raw power is not easy to utilize as entire code parts have to be rewritten using a GPU programming language. Even though high-level standards (e.g. openACC) are able to bring a basic acceleration with a low development effort, it is not simple to get large speedups with these methods. Low-level programming languages are more efficient but different speedups are reported and there is a need for a deep analysis to make the GPU potential more transparent to scientists especially non-experts in HPC.

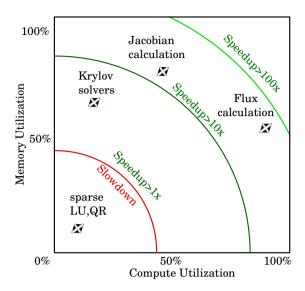

In order to study the GPU acceleration for CFD steady simulations, two in-house CFD solvers have been ported to the GPU; one with explicit and the second with implicit time-stepping. After the porting and the validation of the GPU solvers, the GPU code optimization leads to the identification of a set of key parameters affecting the GPU efficiency. At the same time, both methods have been compared resulting into a performance model and a classification of the GPU acceleration of some CFD operations. The purpose is to enable scientists to take an educated decision concerning the GPU porting of their CPU applications by providing an expected GPU speedup.

In addition to the two GPU CFD solvers that are now integrated into the inhouse design optimization software package, this research provided key elements to reduce the ambiguity about the GPU potential, namely a qualitative analysis and a classification. These tools can help selecting the best candidate for a breakthrough in CFD acceleration. At the same time, this work identified serious limitations in the preconditioning of a linear system of equations and the limit of today iterative matrix factorization methods in terms of stability and convergence. There is a need for a paradigm shift toward inherently parallel preconditioners. The developed tools have been used for the optimization of a compressor and a turbine cascade resulting into a faster optimization process on the GPU.

### Acknowledgment

My research work within my Ph.D. started with the project AMEDEO enabling me to meet and exchange with great people, visit many research institutes and access valuable training all over the journey. For that, I am very grateful to my supervisor Dr. Tom Verstraete who believed on my small but growing GPU expertise back on 2013. Tom has done a fantastic supervising work with me by first giving me the freedom to act in my research but then closely checking my results. Moreover, I would like to thank Juliet Jopson for successfully coordinating the AMEDEO project and making the administration part much easier for all research fellows within the project. I would like also to thank Prof. Harvey Thomson for offering me a secondment within his team at the University of Leeds. During the short stay, I cooperated with Nicolas Delbosc from whom I learned so much about GPU performance assessment. I am very grateful to you Nic. I am thankful to all of AMEDEO people and a special thank to Dr. Roeland de Breuker for putting me in contact with Prof. Kees Vuik who later become my Ph.D. promoter.

Prof. Vuik knows how to get a student fully motivated and prepared for the challenges within a Ph.D. project. You name a software library or a research facility and he would surely know someone to contact to make the stuff happen that you asked for (e.g. DAS-5, SURFsara, Paralution). For all the time and the effort you invested in my project I am really thankful.

I would like also to thank the graduate school at TU Delft for the enriching courses and the possibility they bring to meet other Ph.D. students and exchange about ideas, challenges, views, fears, and ambitions. I would like to thank Deborah Dongor for helping me through the process of being an external Ph.D. student.

My work would not have reached the maturity it has now without the constant support of the people of the TU department in VKI. My supervisor Tom and Prof. Tony Arts were always supportive when it comes to attending conferences and presenting my work. I owe a lot of what I learned during these last years to my colleague Lasse Müller. Besides the valuable discussions he provided me with the CPU version of the CFD simulation, the base of all my work. I am grateful to my colleague Christopher Chahine who taught me a lot of practical knowledge in design optimization. I would like to thank Roberto with whom I cooperated the last months and learned a lot. Eager to continue the collaboration. For the rest of the TU group I

hope we will renew our biweekly department meeting to continue exchanging about our latest results.

I would like to thank all the computer center staff here at VKI and also Christelle and Evelyne for supporting my numerous requests for papers and documentation. I am thankful to the VKI administration and especially to Dirk who made all administrative procedures so easy for me at the beginning of my Ph.D. and after him, Simone took over and facilitated all the paper work for me.

I would like to thank Dr. Andrea Lani and his team first, for the fruitful discussions over the best use of the GPU but also his patience for my long benchmark using his machine as a reference CPU for all my thesis and my publications.

I am also deeply grateful to all committee members for the time and effort invested on evaluating my manuscript.

I would like to thank my office mates: Guillaume, Miguel, and Zdenek. With those guys (and especially after Davide left :D), the office was well stuffed for a nice science journey.

There are some people without them I would not have reached the point to start a Ph.D. That is my father who taught me to be curious and enthusiastic about nature and engineering and my mother who taught me discipline and integrity. Being the youngest member in my family I learned a lot from my sisters: Nejla, Khaoula, Kaouther, and Amina. To all of them, I am very thankful.

Finally, thank you Meyssen for your unconditional support and the happy moments we spent together. You made it possible for me to face the challenges in the Ph.D. and beyond.

### Introduction

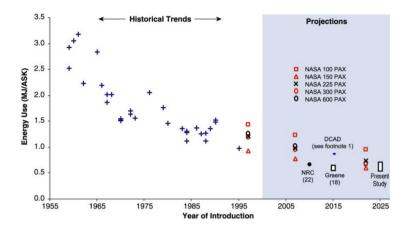

Modern aircraft have a reduced CO<sub>2</sub> emission and fuel consumption compared to airplanes of last century. Figure 1.1 shows a threefold decrease of aircraft energy usage per Available Seat Kilometer (ASK) from the fifties to the end of the twentieth century. This is the result of a continuous optimization process of the whole aircraft including the topology, the shape, and materials. It is worth to note also that roughly 80% of the reduction in the specific fuel consumption is due to advances in gas turbines and propulsion in general. This effort is expected to increase further as a report by the European Commission † highlights the necessity of a stronger reduction of the emissions for future airplanes in order to reduce the environmental impact. The potential to further improve the efficiency of a design is decreasing with years (e.g. in 1960 it was much easier to reduce 1% of the specific fuel consumption (SFC)<sup>‡</sup> than it is now), while the optimization effort increases dramatically. In the last decades, two major developments are projected to become key enablers to further improve modern designs: automated high-fidelity optimization and High-Performance Computing (HPC). These two topics will be presented in this chapter in addition to the research objectives and the outline of the thesis.

## 1.1 CFD and automated optimization

Over the past 3 decades, the design process for turbomachinery applications has seen a large evolution. Nowadays, all components are evaluated through simulations using Computational Fluid Dynamics (CFD) and Computational Structural Mechanics (CSM) before being build. Unlike the traditional trial-and-error design approach, which relies on an extensive testing phase [Vassberg and Jameson, 2006], the process of virtual design allows for a large number of adaptations of the design leading to a higher performance. The next evolution currently enrolling within this process of virtual design is to rely on an automatic optimization algorithm to modify the design. These optimization algorithms can find a better-performing design in

$<sup>^\</sup>dagger http://ec.europa.eu/transport/sites/transport/files/modes/air/doc/flightpath2050.pdf$

<sup>&</sup>lt;sup>‡</sup>SFC is a measure for the efficiency

Figure 1.1: Aircraft energy usage per Available Seat Kilometer (ASK): historical trends and projections (source:[Lee et al., 2001]).

a reduced time with minimal intervention of the designer. The algorithm actually decides automatically on modifications to be made on the shape based on experience gradually build during the design process. The aim of the modifications is to maximize (or minimize) a certain objective related, for instance, to the efficiency (or to the losses).

While the existence of a better-performing design is case-dependent, reaching this design depends on how "smart" the optimization algorithm is and how much computational budget is available. First, more details are given of the optimization algorithm and later in the next section, the computational budget will be addressed.

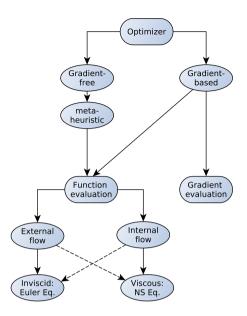

Optimization methods can be roughly classified by the information required by the evaluation process. While zero-order methods require only the function evaluation of the objective, first-order methods require additionally the gradients of the objective function with respect to all design variables. First-order methods, such as steepest descent and conjugate gradient, have a better convergence behavior at the expense of computing the objective derivatives. The gradients can be computed with a repeated function evaluation within a finite difference scheme or through the adjoint state method. The gradient-based optimization improves, in general, a single design using the gradients and exposes, therefore, a reduced parallelism. Since this work studies mainly the effect of the massive parallelization on the design optimization, it focuses only on gradient-free optimization methods.

Most of zero-order optimization methods are nature-inspired and based on metaheuristics. Some gradient-free methods improve a single design by exploiting its neighborhood in the design space through a local search such as Tabu search [Glover, 1989] and simulated annealing [Talbi, 2009]. Other zero-order methods are populationbased such as evolutionary algorithms [Fonseca and Fleming, 1995] and swarm intelligence [Talbi, 2009]. These methods explore the design space with a multitude of interacting and evolving designs. Explorative algorithms try to uncover within a few iterations a wide region of the design space, while exploitative algorithms tend to focus on a limited area of the design space (e.g. the neighborhood of a given design).

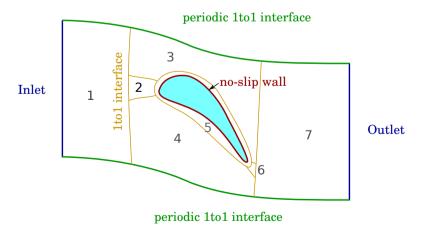

The optimization of an airplane wing, for instance, involves external flow aerodynamics and in general targets a higher lift and a lower drag, which results in a better usage of the power delivered by the jet-engine. The delivered power itself can be increased through an optimization of the engine using internal flow aerodynamics. While more resistant materials and clever cooling methods brings the engine to operate at higher temperatures and deliver thus more power with a higher efficiency, the optimization of the shape of the turbine and compressor blades mainly reduces the losses for the flow through the engine. In aerodynamic optimization, a design is parameterized, in general, using some geometric parameters that control the shape of a blade such as the thickness, the blade chord and the blade angles. Some of these parameters can be chosen as design variables. All possible combinations for these design variables, which are allowed to vary within a fixed interval, form the design space. This space can be constrained by some conditions proper to the case such as a minimum thickness.

The final design will be validated with wind tunnel experiments to check the accuracy of the numerically delivered results. In order to reduce the gap between the experimental results and the simulations, the discretization of the flow governing equations should incorporate most of the relevant physical phenomena. Euler equations, for instance, are limited to inviscid flows [Anderson, 1995] neglecting all shear stresses and heat conduction terms [Hirsch, 2007], while Navier-Stokes equations cover the viscosity and the flow turbulence as well. CFD solvers need also to account for the turbulence, which is a complicated multiscale phenomenon. Some methods, such as the Reynolds-Averaged Navier-Stokes approach, rely on models to reproduce the effect of the turbulence. Other methods, such as the Large Eddy Simulation (LES), resolve the largest turbulent scales, while modeling the smaller scales [Pope, 2001] and the Direct Numerical Simulation (DNS) resolves all scales of the turbulence. It would be tempting to use DNS in order to reach the best possible numerical precision. For transonic conditions, this method remains out of reach of current high-performance systems as the execution time on conventional systems is proportional to  $Re^3$  [Pope, 2001]. As a result of its lower computational cost and reasonable accuracy under attached flow conditions, RANS simulations are nowadays widely established in academia and industry.

In a context of a gradient-free optimization where the search for the optimum requires many evaluations, RANS simulations need to be accelerated to maintain feasible turnaround times. Three types of algorithm optimizations [Thevenin and Janiga, 2008, p.14] are possible to improve the convergence of gradient-free optimization methods: mathematically, physically and computer science based optimizations. The first two methods accelerate the convergence of the optimization toward better designs with a given computational budget, while the last adapts the optimization to a higher computational power. Physically-based optimization reduces the complexity of the objective function evaluation by replacing it with a less complicated model (metamodel) that generates a faster but less accurate design evaluation. A mathematical-based optimization takes advantage of preconditioner and multigrid techniques to accelerate the convergence while solving systems of linear equations. Finally, a computer-science motivated optimization consists of using

high-performance computing to accelerate the execution of numerical simulations. The latter type of optimization is the central focus of this work and will be further discussed in the next subsection.

## 1.2 High-Performance Computing

Accelerating simulations within a design optimization can bring two advantages: (1) more designs can be evaluated for the same time budget leading to a wider exploration of the design space or alternatively, (2) higher-fidelity simulations are accessible for the same time budget.

Getting an application to run faster can be done in different ways. Straightforward methods include, for instance, a hardware upgrade (e.g. a higher CPU rate) or the use of a more advanced compiler, which does more automatic code optimization. A more promising method consists of parallelizing the application. The latter is not trivial but ensures a higher acceleration when adequately used. The parallelization, in some cases, can require a simulation code to be partially or totally rewritten (e.g. CUDA<sup>†</sup>, openCL<sup>‡</sup>). In other cases, few added lines could be enough to enable a parallel execution of a portion of a code, in general for/while-loops (e.g. OpenMP<sup>§</sup>, OpenACC<sup>¶</sup>). Accessing high accelerations using any of the above introduced methods requires definitely a sound knowledge of the used hardware and the specificities of the application to port.

The high performance systems can be classified following the memory architecture as depicted in Figure 1.2. The two main architectures are the shared-memory and the distributed-memory systems. For the shared-memory architecture, a set of processors shares the same memory contingent. Current popular architectures such as dual-core and quad-core CPUs belong to this group. OpenMP [OpenMP, 2013], an Application Programming Interface (API), handles the parallelization in these systems. Few simple compiler directives (#pragmas) surrounding sequential for-loops divide automatically the work between available cores and every core processes a part of the loop. The communication among processors is very simple since they all share the same memory contingent. The maximum available number of cores and the memory capacities for this system are, however, too low to cover large-scale problems (maximum by Xeon Phi with 60 cores [Jeffers and Reinders, 2013]).

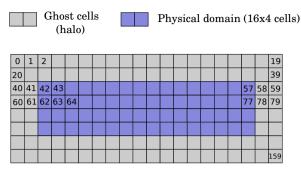

In the distributed-memory configuration, better known as clusters, every processor has its own memory. The communication between processors occurs through the Message Passing Interface (MPI<sup>||</sup>). A decomposition of the computational domain is essential for the parallelization on distributed-memory systems. Every processor contributes to the solution of the simulation by solving a part of the computational domain. A high number of cores (e.g. cluster of CPUs) could speed up the whole process significantly. But the parallelization increases also the programming burden, since the designer has to distribute the computational work among the available

<sup>†</sup>http://docs.nvidia.com/cuda/cuda-c-programming-guide/

<sup>†</sup>https://www.khronos.org/opencl/

<sup>§</sup>http://www.openmp.org/

$<sup>\</sup>P$ https://www.openacc.org/

http://mpi-forum.org/

Figure 1.2: Difference between shared and distributed memory architecture.

CPU processors and regulate the communication. For a realistic application, a large number of cores is essential and MPI is the most implemented paradigm on today HPC systems. Hybrid systems, consisting of a cluster of shared-memory systems, are getting more and more popular. The most powerful HPC systems nowadays are hybrid [Strohmaier et al., 2016] while using in every cluster node not only standard CPUs but also accelerators such as Field Programmable Gate Arrays (FPGAs) and Graphics-Processing Units (GPUs).

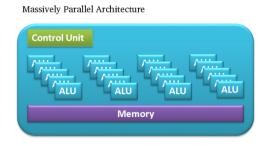

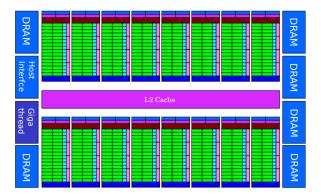

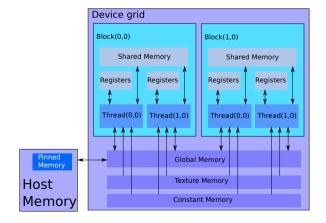

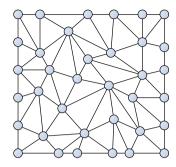

The GPUs can be considered as a shared-memory system since a number of multiprocessors are connected to the same device memory as depicted in Figure 1.3. In total, a GPU contains hundreds of cores mostly dedicated to arithmetic operations, called Arithmetic Logic Units (ALUs). Compared to a CPU core, a GPU core is less powerful. A GPU includes, however, a large number of these cores, which combined result in a higher computational power. The second advantage is the specialization of the GPU cores. While CPUs are inherently responsible for a wide spectrum of

Figure 1.3: Massively Parallel Architecture.

tasks requiring a large cache capacity and an advanced flow control, a GPU is mostly dedicated to floating-point arithmetic calculations. This is reflected in the achieved high computation performance measured in float operations per second (FLOPs).

Today's GPUs evolved from graphics cards installed in most computers starting from the eighties. A graphics card is a complex electrical circuit that processes graphical data sent from the CPU to render and visualize it on the monitor with increasing quality and refreshing rates. A high pressure on graphics cards for fast refreshing of pictures (mainly for video-gaming) caused the spectacular increase of the computational power reflected by the large number of cores packed in one card.

The high computational power attracted scientists and engineers looking for lowcost high-performance alternatives to speed up their applications. To use these first graphics cards, scientists had to present their problems as graphical problem to the card, which implied a change to the data storage and the programming language. The term GPGPU, which stands for General Purpose Graphics Processing Unit, was established for this type of use of the graphics card. In response to this emerging demand, NVIDIA released in 2007 the first fully programmable open graphics processing units [Lindholm et al., 2008] in a C-based programming language called CUDA. At the same time, AMD released its programmable GPU with OpenCL. The programming model CUDA is specialized for NVIDIA GPUs whereas OpenCL can be run on AMD and NVIDIA GPUs. This portability has a price on the programming overhead and the peak performance gain [Fang et al., 2011]. Programming GPUs in a more generic way is possible with openACC, a similar approach to OpenMP. However, accessing high speedups on OpenACC is not trivial [Christgau et al., 2014] and the directive is open but the compiler for this directive is under commercial license, which reduces its impact on the scientific community compared to CUDA or OpenCL. In addition to that, GPU Libraries can assist developers to speed up there applications since many established CPU libraries have their equivalents for GPU such as CUFFT †, CUBLAS ‡ and CUSPARSE §.

## 1.3 Research objectives

Many algorithms are nowadays already intended to run in parallel when developed [Dongarra, 2016] but running an algorithm efficiently in a massively parallel device such as the GPU is still challenging. For CFD applications, speedups ranging from one to two orders of magnitude or even beyond are reported in the literature [Niemeyer and Sung, 2014b]. Different speedups are also reported for design optimization, which will be detailed in Chapter 3. At the same time, these accelerations are severely criticized by some researchers [Lee et al., 2010; Vuduc et al., 2010] highlighting a set of limitations for the GPU and judging the reported large speedups as artificially inflated by choosing an underoptimized CPU reference code.

Under these discordances of case-dependent and sometimes contradicting speedups, it is difficult to estimate a plausible GPU acceleration for a new application. The objective of this doctoral thesis is, therefore, to make the GPU potential more

<sup>†</sup>http://docs.nvidia.com/cuda/cufft,accessed 6/2017

<sup>&</sup>lt;sup>1</sup>http://docs.nvidia.com/cuda/cublas,accessed 6/2017

<sup>§</sup>http://docs.nvidia.com/cuda/cusparse,accessed 6/2017

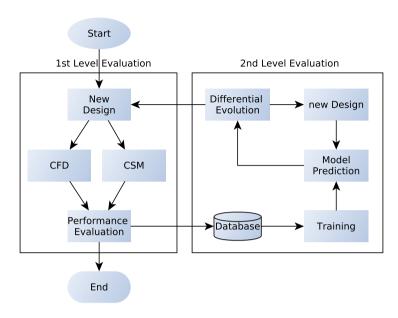

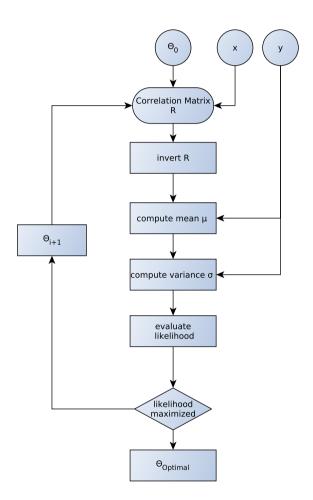

Figure 1.4: Chart of the 2-level optimization in-house tool CADO [Verstraete, 2010].

transparent to the design optimization community and CFD users in general. A clearer perception of the GPU potential can help to make an educated-decision about whether porting a simulation or not to the GPU. The scope of the study is limited to steady CFD simulations solving RANS equations on structured meshes within a population-based design optimization framework for turbomachinery applications.

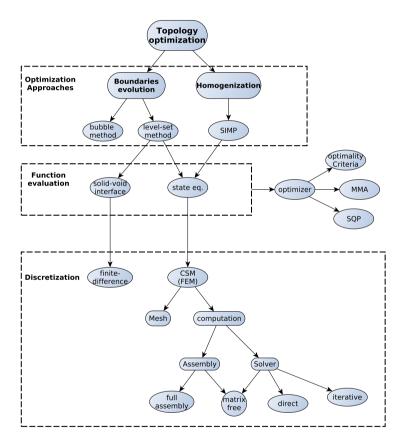

Research activities in design optimization at the Von Karman Institute (VKI) have been started more than 15 years ago. Several innovative algorithms have been developed since, and are currently being used within the design of turbomachinery components in various applications grouped in a software package called CADO [Verstraete, 2010] with its algorithm sketched in Figure 1.4. A key feature of the developed multidisciplinary approach is the use of high fidelity CFD (fluid) and CSM (solid) computations, which constitutes the largest cost of the methodology. A fast interpolation method such as Kriging is extensively used in the 2nd level evaluation to help explore the design space.

The main objective of having a more tangible GPU potential is tackled within 4 steps:

First, a literature survey reported on the main use of the GPU in multidisciplinary design optimizations. The aim is to identify the type of operations delegated to the GPU and to answer the question whether the GPU is used as a workhorse for single-field simulations or as a coordinator of entire optimization algorithms.

- Second, a detailed performance assessment of GPU CFD solvers is performed

with the aim of classifying operations based on exposed parallelism and reached

acceleration. For that purpose, two RANS solvers have been ported to the

GPU: the first with explicit time-stepping and the second with implicit timestepping. The profiler-guided code optimization led to the identification of few

speedup categories for some CFD operations differentiating between stencilbased operation and other operations such as linear system solver iterations

and sparse matrix factorization.

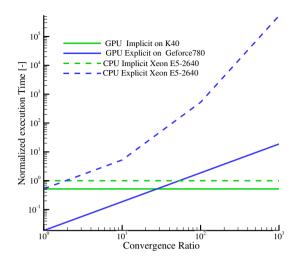

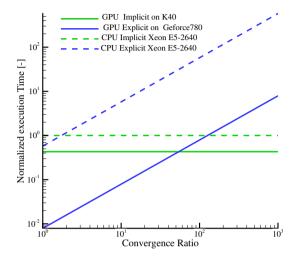

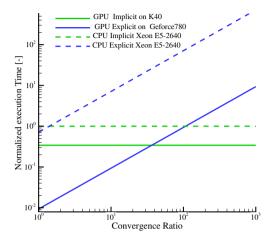

- Motivated by the results of the second step, a third step consists of comparing the explicit to the implicit solver. First a comparison for one flow iteration has been delivered and then a generalization has been intended for a whole simulation by introducing a convergence ratio relating the number of flow iterations of both solvers (explicit and implicit) to reach a stationary solution resulting into a performance model.

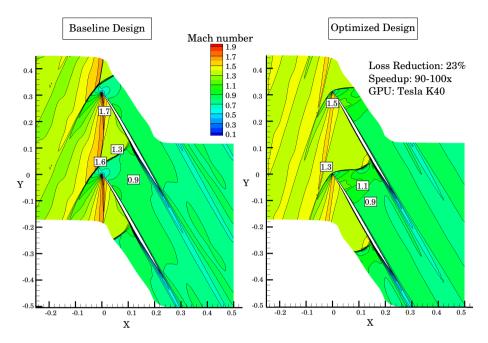

- The last objective concerns the proof-of-concept for a design optimization in a high-end computer with a GPU accelerator. Two test cases are optimized, a compressor and turbine cascade, with the application of the new introduced performance model to identify the fastest alternative (explicit/implicit on GPU/CPU).

### 1.4 Context and outline of the thesis

The work for the present PhD thesis has been started within the EU-funded Project: AMEDEO  $^{\dagger}$  (Aerospace Multidisciplinarity Enabling DEsign Optimisation). The overview of the research conducted in this work is summarized in Figure 1.5 with the problem formulation, the research items and the outcome being linked to the outline of the document.

The GPU has a large computational power which may be very useful for many researchers working in MDO as they rely on time-consuming simulations. Chapter 2 brings the necessary details to situate the GPU within the established HPC architectures. Moreover, it shows the profiler-driven code optimization approach followed in this work to increase the performance of the implemented GPU functions.

Chapter 3 presents a literature survey on the use of the GPU for design optimization. The results of many researchers are reported while observing that the GPU has been used mostly as an accelerator for a single-field simulation (e.g. CFD or CSM) and not used to incorporate the complexity of MDO algorithms. For a single discipline, the literature reports speedups of one to two orders of magnitude, while speedups as a key measure of the GPU performance face some criticism [Lee et al., 2010]. For structural analysis, the GPU has been used to solve the system of equations created by the coupled Partial Differential Equations (PDEs) governing the structural analysis. For the computational fluid analysis, the GPU is very

<sup>†</sup>http://www.amedeo-itn.eu/

#### Problem Statement

#### **Problem**

MDO problems need HPC solutions (e.g. GPU). The GPU potential is case-dependent and controvertial.

#### Research Target

Make the GPU potential more transparent.

#### Research Items

- 1) Literature Review

- Chapter 3

- GPU: single field, no MDO

- Speedups are *case-specific*

- 3) Results Analysis

- 2) Parallel implementation

- Porting and optimizing a CFD solver with explicit time-stepping. Chapter 4

- Porting and optimizing a CFD solver with *implicit* time-stepping.

- Chapter 6

- Classification of different CFD operations based on speedup.

- A qualitative *model* for the explicit/implicit comparison.

- Use of the model within a shape optmization. Chapter 7

#### Outcome Chapter 8

- Explicit solver experience large GPU acceleration (>90x).

- Implicit solver are less prone to the GPU acceleration (<=10x).

- The presented model can deliver an answer on the fastest combination.

- GPU is able to accelerate single-field simulations within MDO.

Figure 1.5: Structure of the work through the thesis.

efficient in running particle-based algorithms [Rinaldi et al., 2012; Zhao, 2008], less for structured meshes within the Finite Volume (FV) scheme and much less with unstructured meshes [Niemeyer and Sung, 2014b].

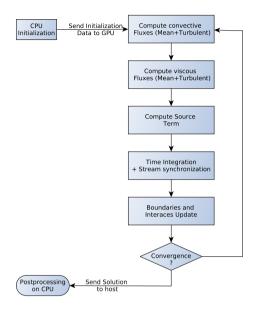

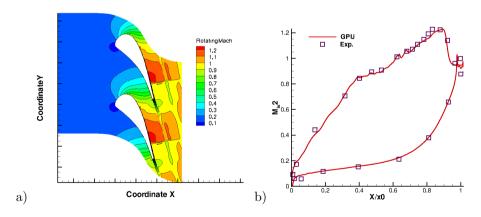

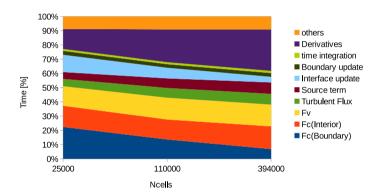

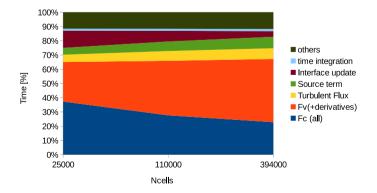

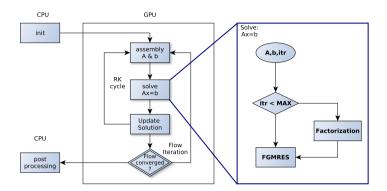

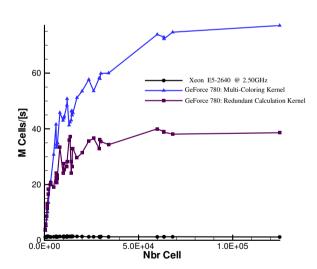

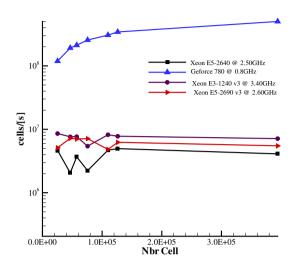

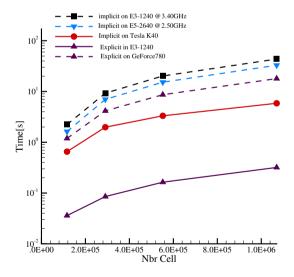

In order to assess more closely the effect of the GPU on single disciplines such as the CFD, an in-house CFD code is ported to run on the GPU. Chapter 4 and 5 present two GPU-based RANS solvers with different time-stepping methods. The first has an explicit time-stepping and experiences two orders of magnitude acceleration on the GPU. The second has an implicit time-stepping and a one order of magnitude acceleration is obtained. The numerical results have been verified against the experimental ones revealing a fair matching that guarantees the accuracy of the new solvers on subsonic and transonic conditions. The code optimization for both solvers led to some key observations on the profiler-driven code optimization for the GPU performance that are presented in Chapter 2. This latter chapter is intended to introduce the concepts used in the analysis of the different implementations for the functions used in both solvers.

Built in a modular way, the CADO optimization software allows to interact with different CFD solvers. The GPU acceleration benefited CADO simply by replacing the CPU-based solver by the new GPU-based one. Speed but also stability of CFD solvers are relevant for the MDO optimization, therefore a comparison of both solvers have been performed concerning speedup, stability, and convergence (see Chapter 6). First, the acceleration per iteration has been observed to be clearly advantaging explicit solvers. Secondly, the convergence rates, which are largely in favor of the implicit solver, have been incorporated in the comparison. Both elements are used to build a model, which selects the fastest alternative for a given convergence ratio.

In Chapter 7, the GPU-enhanced optimizer has been tested on a supersonic compressor cascade achieving an improvement of 25% in the entropy generation and the entire optimization process has been 90 times faster on the GPU than on a single core CPU. Moreover, the performance of a 1-level and a 2-level optimization algorithms has been compared for the shape optimization of a turbine cascade. The 2-level method consists of a metamodel assisted optimization using Kriging interpolation. The newly introduced performance model served on identifying the fastest CFD solver to be used in the optimization.

## **Graphics Processing Units for High Performance**Computing

Graphics Processing Units (GPUs) originated from the performance-driven video gaming industry and were used as rendering pipelines with the main task of creating 2D representations of 3D-scenes. This implies a large number of floating-point operations per second (FLOPS) for a single video frame. The GPU evolved consequently to devote most of the device capacities to computing rather than sophisticated control logic and memory caching. This chapter treats first some key aspects of the GPU programming, which are essential to understanding the strong and weak points of the GPU and highlights then the performance-driven code optimization for the GPU.

#### 2.1 Introduction

Current GPUs are multi-threaded processors which can be programmed with a C-like language called CUDA †. They are built over a large number of scalar processors provided by a large memory bandwidth. The common trend in the different NVIDIA modern GPU generations (Fermi, Kepler Maxwell and Pascal) is the gradual increase of the memory bandwidth and the computational power while keeping a similar power consumption. Motivated by the large performance advantage of the Kepler card compared to Fermi<sup>‡</sup>, this work is mainly based on the Kepler architecture using the NVIDIA K40c and Geforce GTX 780.

A serial code can be parallelized to run on a GPU by rewriting it using a low-level language (CUDA or OpenCL), using GPU libraries (e.g. thrust, cuSolver etc§) or by using a compiler directive approach such as openACC. The openACC approach delivers easily small improvements but a substantial speedup requires a deep understanding of the low-level workflow of the ported code and at the same time an extensive knowledge of the openACC standard [Rueda et al., 2016]. Low-level

<sup>†</sup>https://docs.nvidia.com/cuda/cuda-c-programming-guide/, retrieved March 2017

<sup>&</sup>lt;sup>‡</sup>Newer architectures were not available at the start of the PhD, 2013

<sup>§</sup>https://developer.nvidia.com/gpu-accelerated-libraries, last accessed June 2017

changes are easier and more intuitive to implement with a low-level language rather than through a standardized compiler directive-based alternative. This work, therefore, combines CUDA with some GPU libraries such as thrust [Bell and Hoberock, 2011], Paralution<sup>†</sup> and CUSP [Bell and Garland, 2015].

This chapter focuses on CUDA C as it reveals the low-level code transformation essential to reach interesting speedups but the conclusions should also apply to OpenCL since both languages are fairly comparable [Karimi et al., 2010; Fang et al., 2011]. Section 2 presents some aspects of the history of GPUs in order to better understand the architectural design of modern GPUs, which is presented in Section 3. Then, the execution model of the programming language CUDA is shortly introduced in Section 4. After these prerequisites, the last two sections present the memory-related and the profiler-driven optimization of the GPU code.

## 2.2 From graphics pipelines to High Performance Computing

The predecessors of today GPUs have been developed in the early 1980's Kirk and Wen-mei, 2013]. The primary idea was to offload the CPU from rendering images on the display and use a dedicated hardware instead. Image rendering is about creating surfaces defined by vertices, which belong to a polygon (e.g. triangles), and use them to color the pixels of the final image that will be sent to the display. The first GPU was called fixed-function graphics pipeline since it had the hardware to rapidly compute vertices and pixel colors. Vertices have a color that is computed by the vertex shader involving neighbor vertices and rather intensive memory operations. The next stage, the pixel shader, creates an image by giving a color to every pixel based on its surrounding vertices. Features intended to improve the images and make them look realistic and sophisticated are performed at this stage, which performs thus many arithmetic computations using few vertices. Every stage has its specialized hardware optimized for fast memory access for the vertex shader and for fast arithmetic operations for the pixel shader. The graphics pipeline has many more stages, which are detailed in dedicated textbooks such by Kirk and Wen-mei [2013].

There has been a drive towards faster and more realistic rendering of 3D scenes in the gaming industry, which obviously led to a high demand for computational throughput. More sophisticated APIs <sup>‡</sup> were created to match the increased complexity of the pipeline such as directX and openGL. Following the developers demand for more flexibility required to cover a wider range of graphics algorithms, the vertices and then the pixel shader have been exposed for programmers. Many other stages (e.g rastering) from the graphics pipeline remained fixed functions.

A load-balancing problem occurs as small surfaces (e.g. triangles) require much more vertex treatment than pixel treatment, while large surfaces offer the opposite workload. The unification of both processors for vertex and pixels, first introduced

<sup>†</sup>PARALUTION Labs "PARALUTION v1.1.0", 2016, http://www.paralution.com

<sup>&</sup>lt;sup>‡</sup>Application Programming Interfaces are a standardized set of routines that enable an application to use a hardware.

by AMD in the Xbox360 [Andrews and Baker, 2006], solved this load-balancing problem. The unification of different stages processors had also the benefit of reducing the development cost of 2 different processors.

General Purpose GPU computing (GPGPU) emerged from 2000 to 2006, when scientists started using the raw computational power of GPUs for numerical problems in different fields. However, they had to adapt their algorithms to the partially programmable GPU. The vertex shader accepts one input in form of a texture image containing vertices coordinates and the only output is a pixel color from the pixel shader. Some researchers managed to get a remarkable acceleration due to the GPGPU as reported in the survey of Owens et al. [2007]. The speedup required, however, an important programming effort as the developer had to use the graphics algorithms and terminology, which appeared to be too restrictive for numeric intensive algorithms.

The real start of GPU computing is related to the release of Tesla processors in 2006 [Lindholm et al., 2008]. Tesla has fully programmable unified processors in addition to the cache memory and load/store units enabling it to handle compiled code. NVIDIA provided also the compiler, the library and the API to make the Tesla card much easier to use for non-graphics applications. The following generation of GPUs (Fermi) has almost no remaining heritage from the original graphics pipeline.

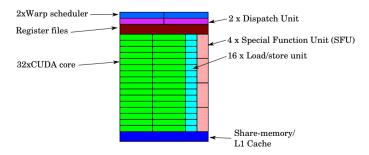

The Fermi card is built around an array of highly threaded streaming multiprocessors (SMs). Figure 2.1 depicts a Fermi SM with 32 CUDA cores (with its arithmetic logic unit), 16 load/store units, 2 schedulers and dispatch units, 4 special function units (responsible for the computation of sine, cosine, etc.), register files and an L1 cache/shared memory. The number of load/store units determines the number of threads that can be served concurrently per clock cycle, here half a warp with a warp defined as a group of 32 parallel threads. With its 2 warp schedulers the SM can execute up to 2 warps at the same time. The Fermi GPU contains 16 SMs, as depicted in figure 2.2, reaching a total of 512 CUDA cores and can run up to 32 warps concurrently. It has also 6 DRAM memory interfaces, which can connect to at most 6 GB of global device memory. The GPU is connected to the host CPU through a PCI express bus. The large number of threads is managed by the *GigaThread* engine that acts as a global scheduler. The shared-memory and L1-cache are very important for a substantial performance gain for some applications.

The GPU Kepler generation, released in 2012, outperforms the Fermi architecture

Figure 2.1: Block diagram of one SM of a FERMI GPU card of NVIDIA.

Figure 2.2: Block diagram of a FERMI GPU card of NVIDIA.

by increasing the number of CUDA cores up to 2880, doubling the precision units and cache size and introducing some new features such as dynamic parallelism and hyper-Q. Dynamic parallelism is about giving a thread the possibility to start a set of sub-threads and is adapted to a multi-level parallelism such as recursive functions. The Hyper-Q allows multiple kernels to run concurrently providing 32 hardware channels for the host to place kernels. As it is a hardware feature no programming is required to take advantage of Hyper-Q. The contribution of this feature can be observed by the profiler as more kernels can overlap with Kepler cards than with the Fermi cards. The card has 15 SMs (less than the Fermi card) but every streaming multiprocessor has been enhanced to host 192 CUDA cores and 64 double precision units. The register files have double size and Kepler has 4 warp schedulers.

## 2.3 GPUs: a throughput-oriented latency-tolerant HPC device

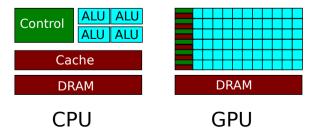

There is a performance gap between CPUs and GPUs in terms of memory bandwidth (amount of data transferred per second) and arithmetic throughput (FLOPS: FLoating OPerations per Second). This is related to the architectural differences between both devices (see Figure 2.3). The conventional multi-core CPU relies mainly on a large and fast memory cache, which serves a small number of cores, in order to reduce the instructions execution time (latency) to a minimum. A significant portion of the transistors is dedicated to the instruction flow control (instruction pipelining, branch prediction † and similar tasks). The CPU cache has a spacial and a temporal locality as data is more likely to be kept in the cache if it is often used (temporal) and if it is close to an often used data (spatial). Neither the large cache memory nor the sophisticated instruction control contributes to the computational power [Kirk and Wen-mei, 2013]. For a CPU, the computational power is provided by a high-speed processor optimized for serial operations and low latency. Moore's law predicted the doubling of the number of transistors in an integrated circuit every

<sup>&</sup>lt;sup>†</sup>A digital circuit to predict the path that will be followed in a branching (e.g. if-else)

2 years [Moore, 1998]. This trend has been carried on until the energy consumption and the heat dissipation reached very high values, known as the power wall [Patterson and Hennessy, 2013, p. 40]. The increase of the clock frequency slowed down also as it is related to the energy consumption and the heat dissipation of the CPU too [Bergman et al., 2008, p.88]. These physical limits caused very powerful single cores to be abandoned in favor of multi-core technology, in which multiple cores are contributing to the computational power of a device.

The GPU, on the other hand, has been designed from the start on as a multi-core technology and disposes of a large number of lightweight processors able to perform single and double-precision computations. The GPU cache is, however, much smaller and disposes only of spatial locality. The gap between CPUs and GPUs concerns also the memory bandwidth. CPUs need in fact to "satisfy requirements from the operating system and the I/O devices which make the memory bandwidth more difficult to increase" [Kirk and Wen-mei, 2013, p.4].

## 2.4 CUDA: a programming language and an execution model

This section explains some concepts of the GPU programming related to the CUDA execution model. An extensive and detailed treatment of the topic can be found in the CUDA user manual<sup>†</sup> and some valuable textbooks [Kirk and Wen-mei, 2013; Cheng et al., 2014; Sanders and Kandrot, 2010; Farber, 2011].

CUDA C is based on the C programming language with a minimal set of extensions to handle the parallel execution and the memory organization. GPUs execute as a device (an accelerator) for a host application on a host CPU, therefore, a CUDA program contains host code and device code. The functions running on the GPU are called kernels and are executed by threads, which are organized in grids of blocks distributed among the streaming multiprocessors. CUDA kernels are launched as follows:

$kernel\_name <\!\!<\!\!Nb\,,Nt\!\!>>\!\!>(var1\;,var2\;,\;\ldots)\;,$

<sup>†</sup>https://docs.nvidia.com/cuda/cuda-c-programming-guide/, retrieved June 2017

Figure 2.3: The architectural design difference between the CPU and the GPU use of transistors.

with Nb the number of thread blocks launched and Nt the number of threads per block. A kernel is usually executed by thousands of threads  $(Nb \times Nt)$ ; though a run with one block of one thread (Nb=1,Nt=1) is equivalent to a serial run on a CPU and can serve as a verification of a written kernel. The GPU starts threads always as a multiple of the warp size. Therefore, the number of requested threads per block should be a multiple of 32 otherwise, the last warp is not fully used and its extra threads are inactive but consume, nevertheless, registers and shared memory space.

Threads have a unique index accessed over threadIdx, a built-in<sup>†</sup> variable. Consecutive indices in threadIdx are handled in groups of 32 threads constituting warps. In a very common CUDA programming pattern, the grid of threads replaces a sequential loop (see Listing 2.1) over a large set of elements. For every thread, the index of its grid and its block are combined to create a unique global identifier as seen in Listing 2.2. Every thread treats a small subset of elements and the programmer should take care of a proper use of the index inside a kernel. Kernel calls are asynchronous since the control is returned to the host CPU immediately after the call, which can then proceed to the next call. A synchronization or a memory copy can force the CPU to wait for the completion of the last called kernel.

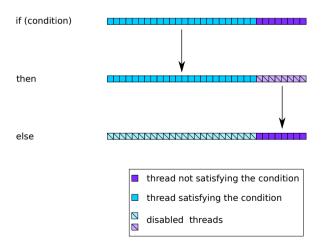

CUDA uses the SIMT (single instruction multiple threads) paradigm to execute instructions within a warp. The same instruction is broadcasted to all threads of a warp for execution but every thread has its own registers and instruction counters. A data dependent conditional branching (e.g. IF-ELSE) can cause threads in the same warp to face different execution paths. The execution is consequently serialized by running first the instruction of the threads of the first path then the instruction of the second path as depicted in Figure 2.4. The possibility of divergence within a warp, called thread divergence, differentiates SIMT from SIMD (Single Instruction Multiple data) processors, which impose strictly the same instruction on a vector of data. Even though it is tolerated, thread divergence is very damaging to the performance since GPUs do not offer the same level of complex branch prediction as CPUs. A fully diverged warp can run up to 32 times slower than a divergence-free warp. Therefore, it is crucial to measure the degree of warp divergence expressed as Branch Efficiency  $(E_B)$ , which is defined as the ratio of the number of non-divergent branches to total number of branches  $(N_B^{\text{Total}})$  [Cheng et al., 2014]:

Listing 2.1: C/C++ code for the loop of the matrix addition.

```

int i,j,idx;

for (i=0; i<N;i++){

for (j=0; j<N;j++){

idx=i+ j*N;

C[idx]=A[idx]+B[idx];

}</pre>

```

<sup>†</sup>pre-initialized variable by the runtime system

Listing 2.2: CUDA code equivalent of the loop for the matrix addition.

```

int i=blockIdx.x*blockDim.x + threadIdx.x;

int j=blockIdx.y*blockDim.y + threadIdx.y;

int idx= i+j*N;

if(i<N && j<N){

C[idx]=A[idx]+B[idx];

}</pre>

```

Figure 2.4: Serial execution of diverged paths within a warp caused by a conditional statement (if-else).

$$E_B = 100 \cdot \frac{N_B^{\text{Total}} - N_B^{\text{diverged}}}{N_B^{\text{Total}}} . \tag{2.1}$$

Multiple threads can access the same memory position in a non-controlled fashion which causes an unpredictable program behavior known as *race condition*. The threads execution order can be controlled by a threads synchronization within a block (\_\_syncthreads()). The synchronization is about inserting a barrier that every thread has to reach before the kernel executes the next instruction. The synchronization of all threads of all blocks requires a call from the host (cudaThreadSynchronize()), which is not possible within a kernel.

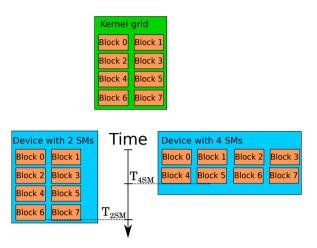

The fact that thread blocks are independent reduces the ability for inter-block communication but it is essential to keep a transparent scalability between thread blocks. Transparent scalability means, in this context, that doubling the number of streaming processors will half the execution time as shown in the example depicted in Figure 2.5.

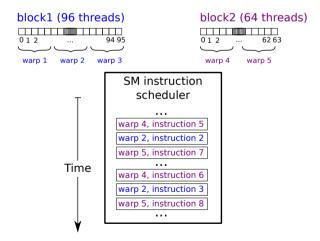

The organization of threads in warps of 32 threads enables to dispatch an idling warp (e.g. waiting for memory access) and schedule a new warp residing in the same SM (see Figure 2.6). This thread swap, called *context switch*, increases the instruction throughput and hides the waiting time for memory loads (memory latency). Unlike the CPU context switch, the GPU context switch is not expensive. The primary difference is that GPU warps have their resources already assigned during the kernel launch and the switch is purely done by the hardware. A CPU needs to copy the state of one thread before loading the state of the new one when switching context. For the GPU, the gain of the context switch is done at the cost of limiting the maximum number of active warps per SM, which cannot exceed the SM resources divided by the single thread consumption. When launching a kernel the threads in a block are sharing the registers (16k/SM for architecture 3.5) and the shared-memory (up to 48kB/SM for architecture 3.5). These are, in general, the limits dictating the number of warps active in the different SMs and is called the theoretical occupancy, which is a measure for the level of thread parallelism.

Warps with secured resources from the SM are called active. But physically active are only the selected warps by the warp scheduler. The non-selected warps could be either stalled, waiting for an argument $^{\dagger}$ , or eligible if they are ready for execution but the hardware is busy. From the active warps, a maximum of 4 can be selected concurrently per SM (for architecture 3.5) and if a warp is stalled the scheduler picks up one of the eligible warps. If a kernel is very demanding of shared-memory such that not even one single block of threads can be assigned to an SM, the kernel execution fails without terminating the host program. CUDA provides thus a function, cudaGetLastError(), to check the status of the last executed call. In the development phase, it is recommended to check the status of every CUDA command by calling the error check function or providing a macro as a safe call wrapper (see CUDA SDK $^{\dagger}$ ). A kernel can fail because of a lack of memory resources or an inappropriate run configuration in terms of number of blocks and grids, while a memory allocation can fail because of a lack of global memory.

<sup>†</sup>a memory transaction or a computation

<sup>&</sup>lt;sup>‡</sup>https://developer.nvidia.com/cuda-downloads, retrieved June 2017

Figure 2.5: A comparison of the execution time of 8 thread blocks in a GPU with 2 SMs and a GPU with 4 SMs.

Figure 2.6: Example of the work done by a scheduler while executing warp instructions.

Warp switching is used to hide the instruction latency, which is defined as the required amount of time from dispatching an instruction until its completion. The arithmetic latency lasting between 10 to 20 cycles is smaller than the memory latency which can reach up to 800 cycles [Cheng et al., 2014]. The estimated number of independent instructions N to hide the latency  $\lambda$  is defined according to Little's law as follows:

$$N = \lambda \cdot \text{throughput.} \tag{2.2}$$

In order to reach the required number of independent instructions N, it is possible to increase the number of warps or/and increase the number of instructions per thread. The first technique is called Thread-Level Parallelism (TLP) and the second is known under Instruction-Level Parallelism (ILP). For memory operations, the throughput is defined based on the clock rate and the memory bandwidth as follows:

$$bandwidth/Clock = throughput. (2.3)$$

The throughput, in general in kB, refers to the in-flight I/O memory operations required to saturate the GPU. For a small N, only few memory operations are started, which deteriorates the reached bandwidth (more in Section 4.2.1).

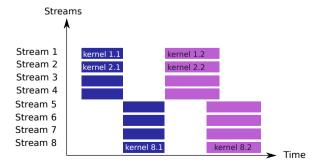

Until now only the fine-grained data parallelism through a grid of threads has been addressed. The GPU offers also a coarse-grained kernel (or task) parallelism by running multiple grids of threads concurrently using multistreams (see Listing 2.3) increasing the number of active warps and consequently the GPU utilization. All kernels and CUDA API calls, seen above, run in fact in a default stream with a stream defined as a sequence of operations executing in the order as issued from the host CPU. At the same time, multistreaming can be used to overlap data transfer and computation.

If a stream synchronization occurs or a kernel is executed by the default stream, the kernels overlapping is interrupted. Indeed, when the default stream executes a kernel or a memory call, all other kernels are in a halt. The hardware resources can also limit the number of concurrent kernels as depicted in Figure 2.7. The GPU keeps running more streams until all resources are assigned to kernels from already launched streams. No additional kernel is able to run from the rest of the streams until the first set of kernels finishes executing.

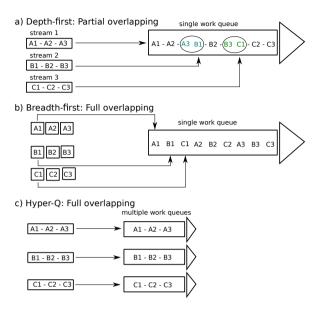

Fermi cards have only one hardware work queue, through which all launched kernels on all streams need to transit. Filling one stream after the other with kernels and API calls (depth-first approach [Cheng et al., 2014, p. 282]) creates a false dependency in Fermi processors. Only the last kernel of a stream and the first kernel of the following stream are independent and thus can overlap (see Figure 2.8). A software approach to solve the false-dependency problem is to make a breadth-first filling of streaming: every stream should have received a command to execute

Listing 2.3: Example of a use of streams with kernels.

```

for(i=0;i<Nstreams;i++) {

cudaStreamCreate(streamArray[i]);

kernel_name<<<threads,blocks,0,streamArray[i]>>>(varibales)

}

```

before any stream gets a second command. This increases the kernels overlapping on Fermi cards to its maximum. NVIDIA proposed a hardware fix for this issue on the Kepler cards by a mechanism called HYPER-Q. Hyper-Q allows up to 32 hardware work queues<sup>†</sup> and thus any case with false-dependency on Fermi cards runs with maximum overlapping on Kepler GPUs. However, breadth-first approach is always advisable. The multistreaming feature is found to be crucial in order to reach interesting performance gain on the GPU (Cf. Section 4.2)

## 2.5 Memory hierarchy of the GPU

The memory hierarchy for the CPU-GPU system proposes different levels of speed and size for every type of memory (see Figure 2.9). The capacity increases from register and cache memory to global and system memory but so does the latency. An efficient use of the available memory levels can leverage the performance of a program to reach a maximum, which is dictated by the hardware limitations. No instruction can be executed, for instance, if a warp is stalled waiting for a variable to be loaded while all load/store units are busy. Therefore, the instruction-level parallelism can not be very beneficial if a kernel is not making good use of the possible memory types.

In general, the system memory residing in the CPU contains the entire data of the simulation. The data that will be needed by the GPU should then be moved to the device global memory which is of the order of few GBs (e.g. Tesla K40 has 12 GB) for a single GPU. This implies that the GPU could solve a problem slice by slice with every slice not exceeding the global memory capacities. Since the PCI bus is relatively slow, the communication between the host CPU and the device GPU has to be kept minimal and small data transfers are faster when grouped together and moved in one shot. Moreover new technology such as NVlink<sup>‡</sup> can further leverage this issue. The data residing in the global memory has higher access latency than the data residing in a cache or a register. Moreover, the access itself to the global memory

<sup>&</sup>lt;sup>‡</sup>more than 80Gb/s memory bandwidth http://www.nvidia.com/object/nvlink.html

Figure 2.7: Illustrative time line for the execution of 16 kernels distributed over 8 streams with the SM resources limiting the concurrency to 4 kernels.

$<sup>^\</sup>dagger The number of hardware queues can be accessed/changed in the environment variable CUDA_DEVICE_MAX_CONNECTIONS$

Figure 2.8: Illustration of the multistream execution of a set of kernels highlighting the amount of overlapping with (a) depth first approach, (b) breadth-first and (c) Hyper-Q.

Figure 2.9: Block diagram of the host and device software memory organization.

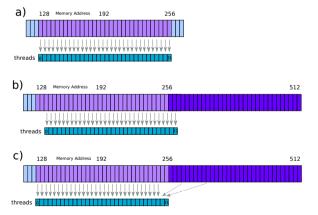

should follow certain patterns to guarantee the best memory bandwidth. The GPU loads an entire word<sup>†</sup>, when a thread accesses a memory position, and the loaded word is broadcasted to all threads of the warp. If the next thread within a warp accesses the next memory position, it is very likely that it is in the already loaded word. The memory transactions of the two threads are grouped or *coalesced* into one transaction. The line size of the L2-cache, by which all global memory accesses are migrating, is 128 bytes, which is optimally used if every thread in a warp requests consecutive 4 bytes. A second key technique is the alignment, which is guaranteed for requested addresses being a multiple of the cache line size. Figure 2.11 depicts first a case of an ideal access then two cases of misaligned and uncoalesced accesses. The alignment makes sure that the minimum number of words is loaded per warp. The misalignment can cause two words to be loaded for one access, while the uncoalesced access can load up to 32 words for one access depending on the scattering of the memory accesses within a warp.

The number of transactions required for a single memory load depends on the coalescence of the access and the data alignment of the transactions [Cheng et al., 2014]. The profiler can compute the average number of global memory load transactions performed for each global memory load. A practical case of storage in global memory is to transform a multi-dimensional array into one-dimensional long array. In a case of a 3D array accessed by the indices i, j and k with maximum values set to IMAX, JMAX and KMAX respectively, the index is as follows:

```

array[i+j*iMAX+k*iMAX*jMAX]=array[i][j][k];

```

The case of mapping the GPU threads to i, j and k is considered (see Listing 2.4). In order to keep the coalesced access, the thread mapping should follow the 1D array indexing with iMax, jMax and kMax set equal to IMAX, JMAX and KMAX respectively. This means a kernel should alter an uninterrupted set of data. In case a kernel is updating only selected parts of the data with some interruptions (see Figure 2.10 for an example), the thread partitioning does not map fully the storage layout and some warps will have uncoalesced access as a jump occurs in the memory accesses. The fact that some data is not used can affect also the alignment since the first accessed memory position is not guaranteed to be a multiple of the L2 cache line size. In that case, the global memory storage/load efficiency decreases from the ideal 100% (for loading/storing a double precision variable). The number of instructions per thread can improve the throughput, even if the added instruction provides uncoalesced accesses. The weight of one code optimization technique against another

Listing 2.4: An example [Delbosc, 2014] of mapping of threads to 3 iterators ij and k.

<sup>&</sup>lt;sup>†</sup>A word is a piece of data with a fixed-size managed as a unit by processor

is thus case-dependent.

The use of registers is largely controlled by the compiler and the user can put a limit on the maximum amount of registers in general or for a certain kernel. The rule of thump is that all variables are stored in registers except large arrays. Registers are a fast-access memory but they are also limited for an SM and their overuse by a kernel limits its theoretical occupancy. If a kernel uses more registers than allowed by the hardware (63 for Fermi and 255 for Kepler GPUs) the excess is moved to the local memory, which is local to the thread but resides in the GPU slow global memory. This is called *spill-over* and should be avoided in general. The data in local memory is cached in L1 per SM and L2 per device. The L1 and L2 caches are rather hidden from the user and the accessible caches are texture and constant memory. Constant memory, for instance, is adapted to store read-only variables that are required by all threads in a warp. From practical experience, it has been observed in this work that the L1-cache combined with compiler optimization makes the effect of the use of constant memory negligible for CFD applications.

The shared memory can be used to reduce the use of the global memory by loading a subset of the data. The threads in a block can work on this sub-data and load it back to the global memory at the end of the procedure. For more details to shared memory, consider the CUDA user manual and some textbooks ([Cheng et al., 2014, p. 203], [Kirk and Wen-mei, 2013, p. 95])

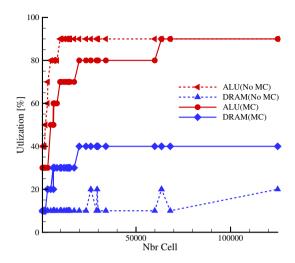

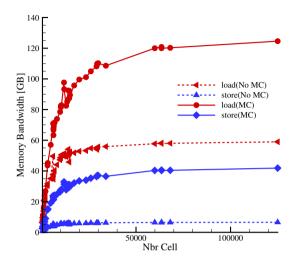

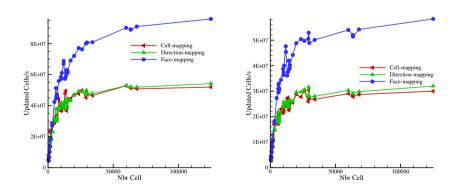

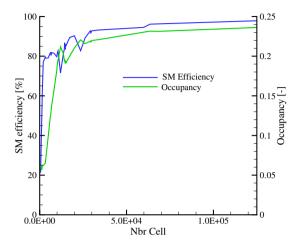

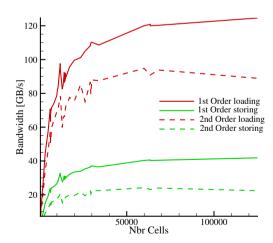

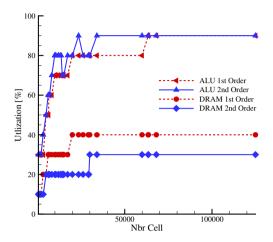

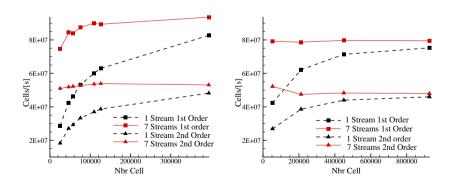

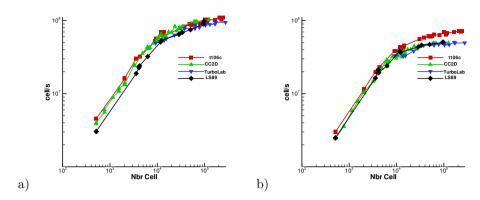

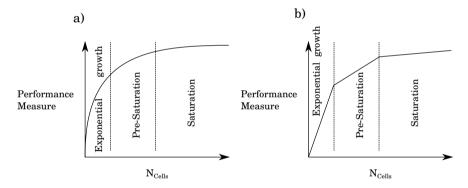

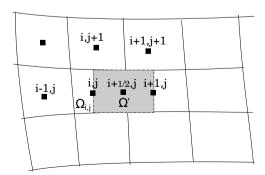

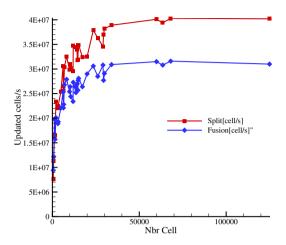

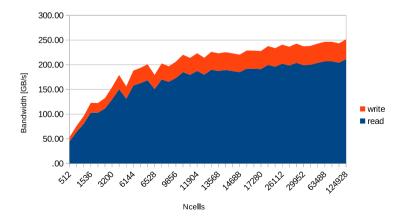

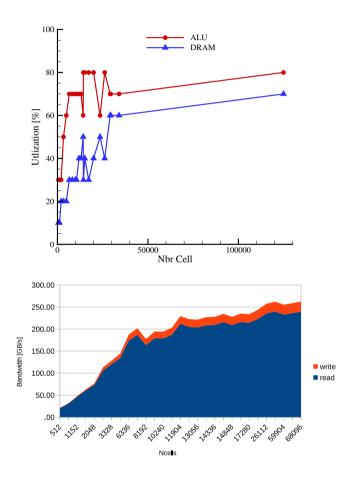

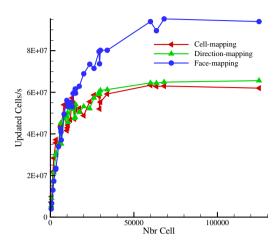

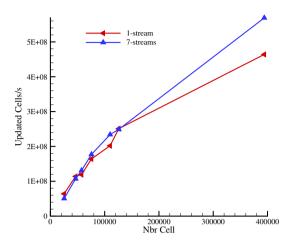

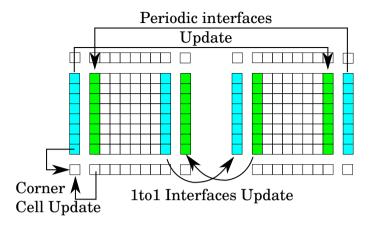

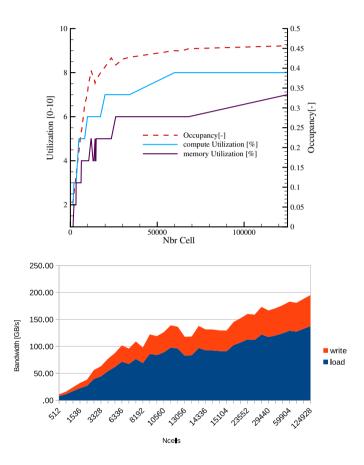

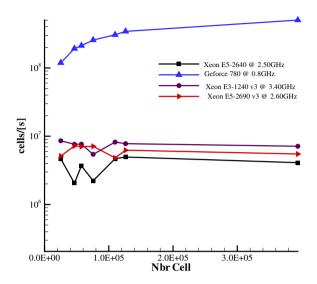

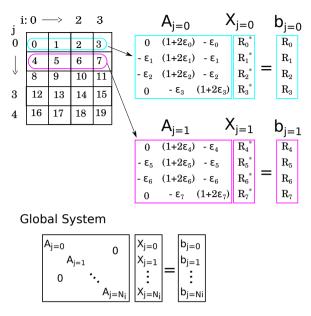

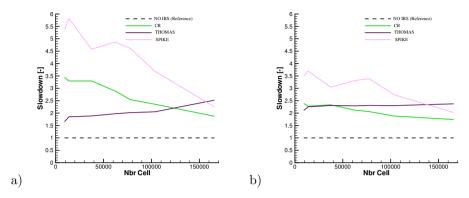

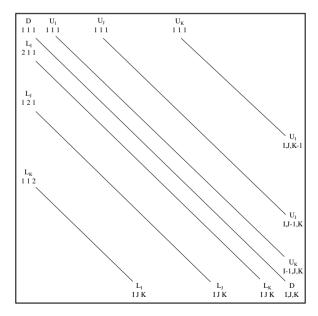

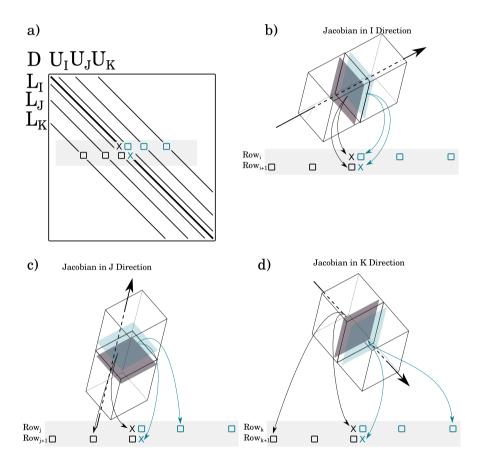

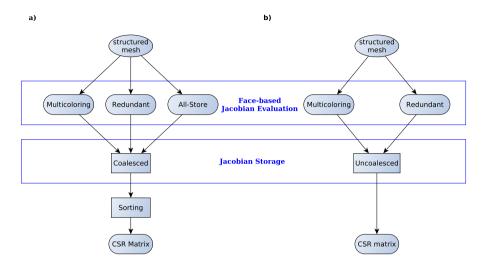

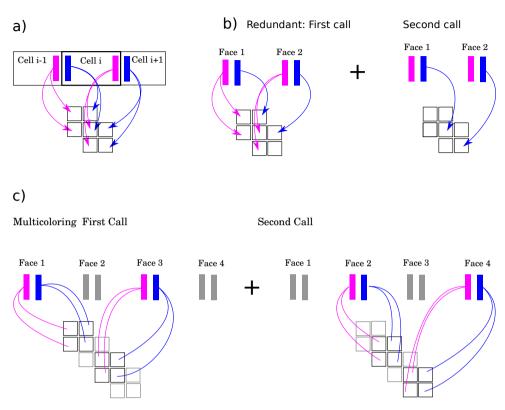

## 2.6 Profiler-Driven code optimization